|

Due date: On or before Monday, April 28, 2025 Absolutely no copying others’ works |

Name: ___________________________ |

- Upload the completed homework to the section of “COVID-19 Exams, Homeworks, & Programming Exercises” of Blackboard.

- The purpose of homeworks is for students to practice for the exams without others’ help, so the penalty of mistakes will be minor.

- Without practicing for the exams properly, students would not be able to do well on the exams.

- Use the figures in slides, instead of the textbook, to answer the questions in this homework.

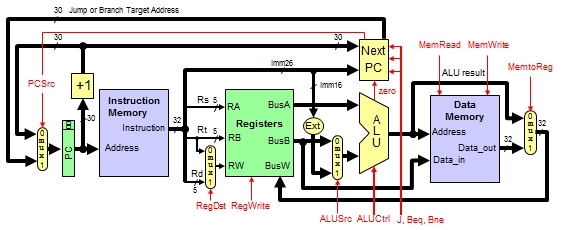

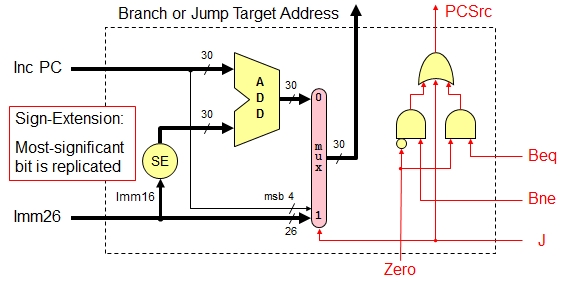

- The following figures are from the Slide 12.10 and will be used in this homework:

- Assume that the logic blocks used to implement a processor’s datapath have the following latencies (time needed to do their work):

I-Mem / D-Mem Register File Mux ALU Adder 230ps 120ps 20ps 210ps 140ps Single gate Register Read Register Setup Sign extend Control 5ps 40ps 15ps 35ps 40ps

- “Register read” is the time needed after the rising clock edge for the new register value to appear on the output. This value applies to the PC only.

- “Register setup” is the amount of time a register’s data input must be stable before the rising edge of the clock. This value applies to both the PC and Register File.

- Answer the following questions:

- (10%) What is the latency of an R-type instruction (i.e., how long must the clock period be to ensure that this instruction works correctly)?

†Hint: Find the time for the critical (longest-latency) path as there may have several paths for an instruction.

Ans>- R-type (“

add $t1, $t2, $t3,” e.g.) ⇒ 40 (PC: Register Read) + 230 (I-Mem) + 120 (Register File) + 20 (Mux) + 210 (ALU) + 20 (Mux) + 15 (Register File: Register Setup) = 655 ps

- (10%) What is the latency of

lw?

Ans>lw:

- (10%) What is the latency of

sw?

Ans>sw:

- (10%) What is the latency of

beq?

Ans>beq:

- (10%) What is the latency of an arithmetic, logic, or shift I-type (non-load) instruction?

Ans>- I-type:

- (10%) What is the minimum clock period for this CPU?

†Hint: This is a single-cycle datapath in which all instructions are executed in one clock cycle.

Ans>

- (10%) What is the latency of an R-type instruction (i.e., how long must the clock period be to ensure that this instruction works correctly)?

- Consider the addition of a multiplier to the CPU shown in the above figures in Slide 12.10.

This addition will add 320 ps to the latency of the ALU, but will reduce the number of instructions by 7% (because there will no longer be a need to emulate the multiply instruction).

- (10%) What is the clock cycle time with and without this improvement?

†Hint: The clock cycle time without this improvement is from the answer of above question 1.f.

Ans>- Without improvement:

- With improvement:

- (10%) What is the speedup achieved by adding this improvement?

†Hint: Speedup from the addition = running time without the addition ÷ running time with the addition

Ans>

- (10%) What is the slowest the new ALU can be and still result in improved performance?

Ans>

- (10%) What is the clock cycle time with and without this improvement?