The ALU is the brawn of the computer, the component that performs the arithmetic operations like addition and subtraction or logical operations like AND and OR. This slide constructs an ALU from five hardware building blocks, (i) AND gates, (ii) OR gates, (iii) inverters, (iv) multiplexors, and (v) a 1-bit adder, starting by constructing a 1-bit ALU.

A 1-bit ALU is shown on the right that performs AND, OR, and addition on a and b or ¬a and ¬b.

The multiplexor on the right selects a AND b”a OR b”Operation is 0, 1, or 2.

By selecting ¬a (Ainvert=1) and ¬b (Binvert=1), we get a NOR b”a AND b”. |

|

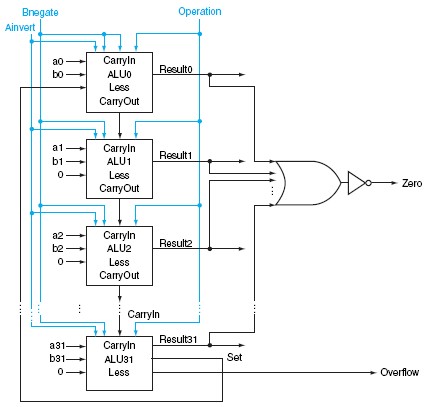

Because the MIPS word is 32 bits wide, we need a 32-bit-wide ALU.

We can connect 32 1-bit ALUs to create the desired ALU as the figure shows.

A single carry out of the least significant bit (Result0) can ripple all the way through the adder, causing a carry out of the most significant bit (Result31).

The Less and Set are used only for slt instruction.

For further details, refer to the Appendix B of the textbook.

|

|