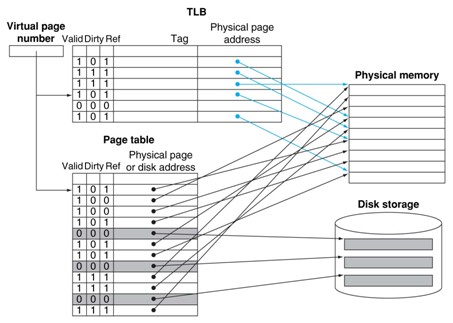

The key to improving access performance is to rely on locality of reference to the page table. The translation-lookaside buffer (TLB) is a cache that keeps track of recently used address mappings to try to avoid an access to the page table. The TLB includes five fields:

- Valid bit: It is on if the page is in memory and the entry contains the physical page number.

- Reference bit: On every reference, the virtual page number in the TLB is checked. If it is a hit, the physical page number is used to form the address, and the corresponding reference bit is turned on.

- Dirty bit: If the processor is performing a write, the dirty bit is turned on.

- Tag entry: Because the TLB is a cache, it must have a tag field, which holds (a portion of) the virtual page number.

- Data entry: It holds a physical page number.

| The page table either supplies a physical page number for the page (which can be used to build a TLB entry) or indicates that the page resides on disk, a page fault. Since the page table has an entry for every virtual page, no tag field is needed. |