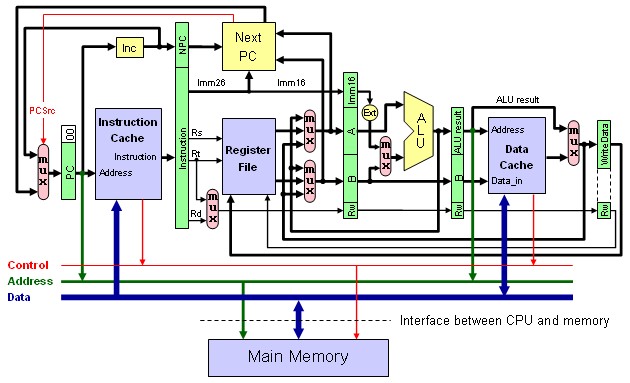

The following figure shows the cache memory, including instruction cache (I-cache) and data cache (D-cache), in a datapath:

To close the gap further between the fast clock rates of modern processors and the increasingly long time required to access DRAMs, most microprocessors support an additional level of caching.

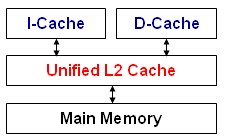

| A multilevel cache is a memory hierarchy with multiple levels of caches. The figure shows a two-level cache, in which the second-level cache is usually on the same chip and is accessed whenever a miss occurs in the primary cache. |

|

If the second-level cache contains the desired data, the miss penalty for the first-level cache will be essentially the access time of the second-level cache, which will be much less than the access time of main memory. If neither the primary nor the secondary cache contains the data, a main memory access is required, and a larger miss penalty is incurred.

| We had a whale of a time (enjoy very much) on holiday. |