Below is a sequence of nine memory references to an empty 8-block cache:

| Decimal address of reference | Binary address of reference | Hit or miss in cache | Assigned cache block (where found or placed) |

|---|---|---|---|

| 22 | 101102 | miss | 101102 mod 8 = 1102 |

| 26 | 110102 | miss | 110102 mod 8 = 0102 |

| 22 | 101102 | hit | 101102 mod 8 = 1102 |

| 26 | 110102 | hit | 110102 mod 8 = 0102 |

| 16 | 100002 | miss | 100002 mod 8 = 0002 |

| 3 | 000112 | miss | 000112 mod 8 = 0112 |

| 16 | 100002 | hit | 100002 mod 8 = 0002 |

| 18 | 100102 | miss | 100102 mod 8 = 0102 |

| 16 | 100002 | hit | 100002 mod 8 = 0002 |

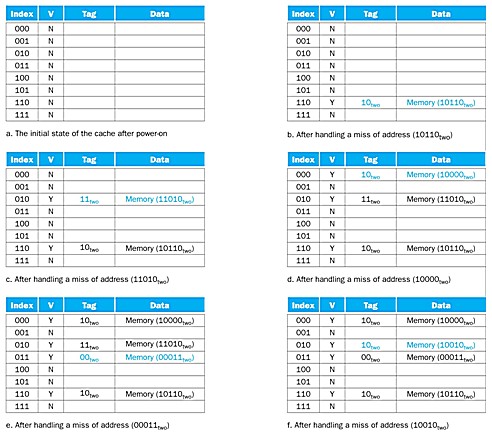

The above references are depicted as follows. The figures show the cache contents after each miss in the sequence has been handled. The cache is initially empty, with all valid bits (

V entry in cache) turned off (N).

The tag field will contain only the upper portion of the address.

The full address of a word contained in cache block i with tag field j for this cache is

For example, in cache f, index 0102 has tag 102 and corresponds to address 100102.

|

|