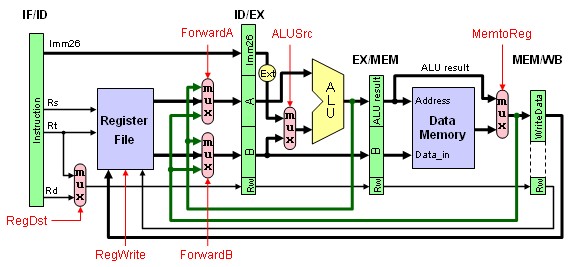

Again, a RAW (Read After Write) data hazard refers to a situation where we refer to a result that has not yet been calculated, for example:

i1. add $2, $1, $3 # $2 = $1 + $3 i2. add $4, $2, $3 # $4 = $2 + $3RAW data hazards could happen at both EX and MEM stages.

- EX Hazard

-

This kind of hazards requires forwarding for operations that use results during the EX stage.

It occurs when

- The current instruction being decoded is in the ID stage and the source register is in the IF/ID register and

- The prior instruction is in the EX stage and the destination register is in the ID/EX register.

Therefore, a pair of hazard conditions are as follows:1a. IF/ID.Rs = ID/EX.Rw 1b. IF/ID.Rt = ID/EX.Rw

where “IF/ID.Rs” refers to theRsregister whose value is found in the pipeline register IF/ID.

Hazard of the above instruction sequence can be detected by Condition 1a.