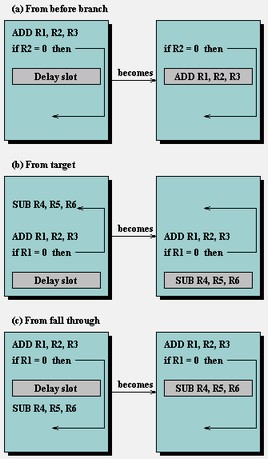

The delayed branch executes one or more instructions following the conditional branch before the branch is taken. This avoids stalling the pipeline while the branch condition is evaluated, thus keeping the pipeline full and minimizing the effect of conditional branches on CPUs. Compilers and assemblers try to place an instruction that always executes after the branch in the branch delay slot. The figure shows the three ways in which the branch delay slot can be scheduled. The left box in each pair shows the code before scheduling; the right box shows the scheduled code.

|

|

Strategies (b) and (c) are used when (a) is not possible. In the code for (b) and (c), the use of

R1 in the branch condition prevents the add instruction from being moved into the branch delay slot.

To make this optimization legal for (b) or (c), it must be OK to execute the sub instruction when the branch goes in the unexpected direction.

For example, if R4 were an unused temporary register when the branch goes in the unexpected direction.