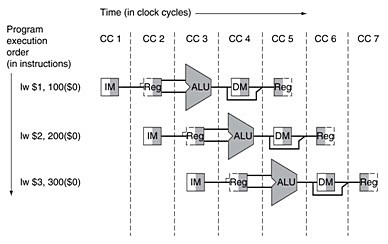

The following figure shows the single-cycle datapath with the pipeline stages identified, which can be mapped onto the datapath from left to right:

- IF: Instruction fetch

- ID: Instruction decode and register file read

- EX: Execution or address calculation

- MEM: Data memory access

- WB: Write back

The figure shows what happens in pipelined execution by pretending that each instruction has its own datapath, and then to place these datapaths on a timeline to show their relationship.

| In the figure, shaded portion is in use, IM represents the instruction memory and the PC in the instruction fetch stage, Reg stands for the register file and sign extender in the instruction decode/register file read stage (ID), and so on. |

|

|

OK, I’ll come to the party Friday. But Saturday it’ll be time to hit the books (study). |