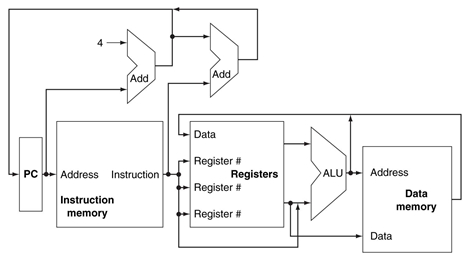

The figure below shows an abstract view of the MIPS subset implementation:

|

- After the instruction is fetched, the register operands used by an instruction are specified by fields of that instruction.

- Once the registers have been fetched, they can be operated on to find a memory address, to compute an arithmetic result, or a compare.

- If the instruction is an arithmetic-logical instruction, the result from the ALU must be written to a register such as

add $t1, $t2, $t3 # $t1 = $t2 + $t3

- If the operation is a load/store, the ALU result is used as an address such as

lw $t1, offset($t2) # $t1 = mem[[$t2]+offset]

- Branches require the use of the ALU output to determine the next instruction address such as

beq $t1, $t2, offset # branch if $t1 == $t2

- If the instruction is an arithmetic-logical instruction, the result from the ALU must be written to a register such as

| The thick lines interconnecting the functional units represent buses, which consist of multiple signals. The arrows are used to show how information flows. |

|