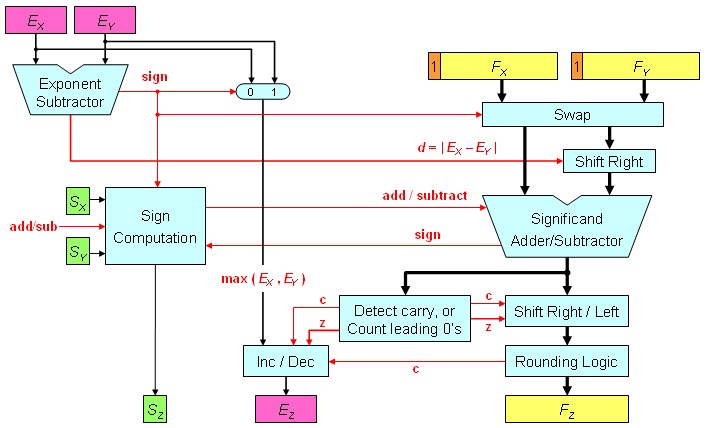

The following figure sketches the basic organization of hardware for floating-point addition and subtraction. Each of the steps of the previous algorithm corresponds to one block, from top to bottom.

- First, the exponent of one operand is subtracted from the other using the small ALU to determine which is larger and by how much.

- This difference controls the three multiplexors; they select the larger exponent, the significand of the smaller number, and the significand of the larger number.

- The significand of the smaller number is shifted right, and then the significands are added together using the big ALU.

- The normalization step then shifts the sum left or right and increments or decrements the exponent. Rounding then creates the final result, which may require normalizing again to produce the final result.

| The project failed, we are back to square one (back to the start). |